FPGA講座-9 assign文と条件式

assign文とは

FPGAの設計で頻繁に使用される構文の一つがassign文です。このassign文を活用することで、簡潔かつ効率的に信号の生成を行うことができます。

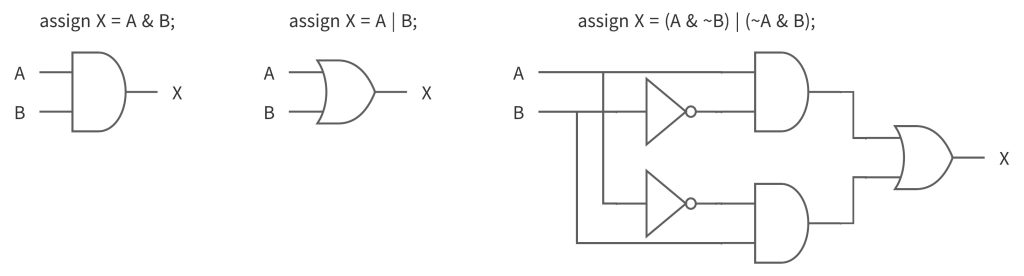

assign文は、組み合わせ回路を記述するための構文です。回路の入力信号に応じて、出力信号をリアルタイムに計算・更新する仕組みを表現できます。具体的には、以下のような形式で記述します。

assign 信号名 = 論理式;

例えば、2つの入力信号”a”と”b”のAND演算を出力信号”y”に割り当てたい場合は、以下のように記述します。

assign y = a & b;

このように、assign文を使用することで、単純な論理演算から複雑な条件式までを効率的に記述できます。

条件式を使用したassign文

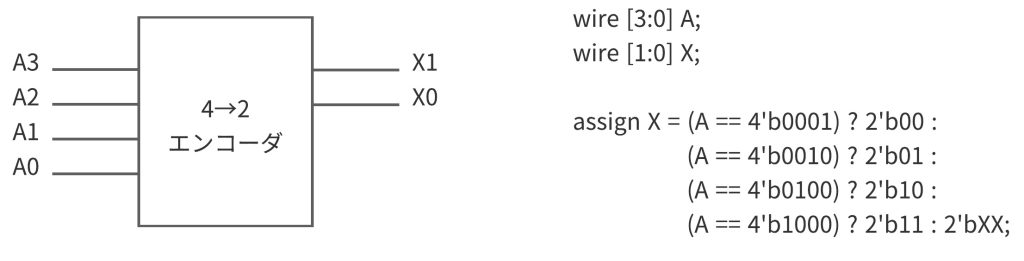

assign文の有効な機能のーつが、条件式を活用できる点です。Verilogでは、条件式を”?”や”:”などの三項演算子で表現します。基本的な構文は以下の通りです。

assign 信号名 = 条件式 ? 値1(論理式1) : 値2(論理式2);

この構文は、「条件が真(true)であれば値1(論理式1)を出力し、偽(false)であれば値2(論理式2)を出力する」という意味になります。

例えば、入力信号”sel”よって、”a”または”b”を出力信号”y”に割り当てる回路を記述する場合、次のように記述できます。

assign y = sel ? a : b;

この記述は、以下の条件に基づいて動作します。

- sel = 1 の場合、y = a

- sel = 0 の場合、y = b

このように、三項演算子を使用することで、条件に応じた信号選択が簡単に記述可能です。

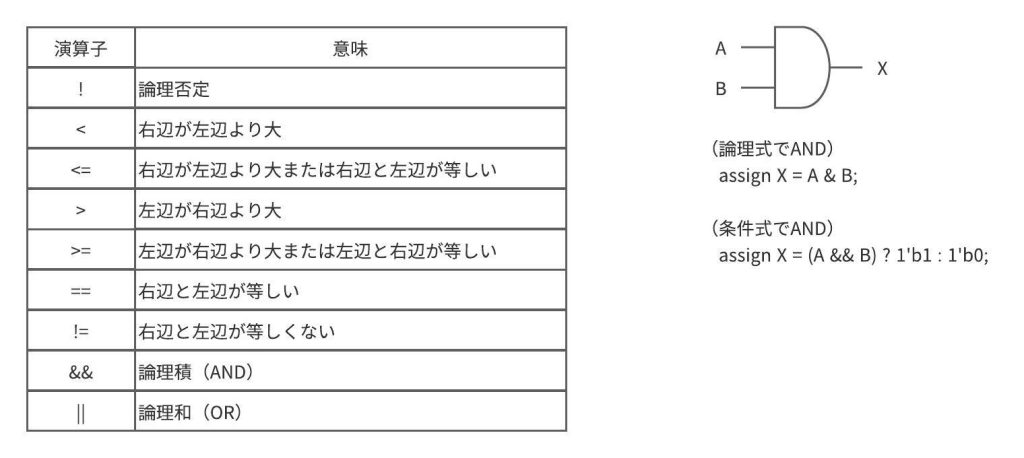

条件式で使用する演算子

条件式で使用する演算子は、図3に図示したように色々と用意されています。これらの演算子を使用して、2つの入力信号”a”と”b”のAND演算を出力信号”y”に割り当てた記述をしてみます。assign文の条件式を使用すると、AND演算は以下のように記述できます。

assign y = (a && b) ? 1’b1 : 1’b0;

AND演算の場合、論理式で表記したほうが簡単ではありますが、上記のように条件式で実現することが可能です。

assign文と条件式は、FPGA設計において非常に便利なツールです。簡潔な記述で複雑な論理回路を表現できるため、効率的な設計が可能になるため、是非活用してみてください。