FPGA講座-5 階層設計とモジュール設計

階層設計

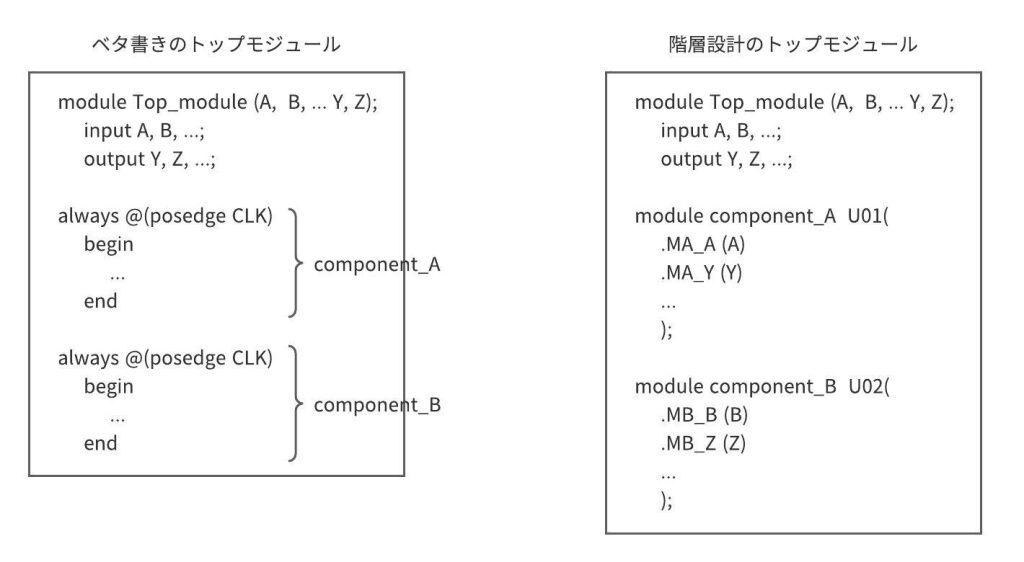

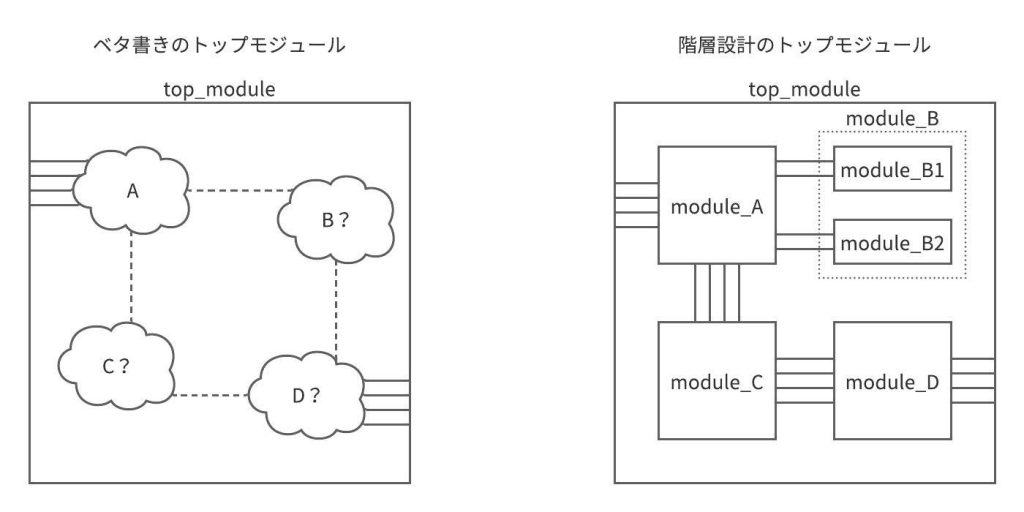

図1に二種類のトップモジュールの記述例を示しています。左側がベタ書きのトップモジュールで右側が階層設計されたトップモジュールです。ベタ書きのトップモジュールは、always文などが直接トップモジュールで記述されています。一方、階層設計されたトップモジュールは、always文などの記述はなく、別のモジュールを読み出しています。イメージしやすいように、図2にブロック図を用意しました。

図2のベタ書きのトップモジュールのブロック図では、コンポーネントAからコンポーネントDまでalways文などで記述されていることを表しています。この場合、結線情報がないため、コンポーネントAとコンポーネントB、C、Dの関係が曖昧で分かり難いと思います。

一方、階層設計のトップモジュールのブロック図では、機能毎にモジュール化されており、結線情報があるため、各モジュール間の関係性が明確に理解できます。回路規模が小さい場合はトップモジュールにベタ書きしても問題ないのですが、回路規模が大きい場合は階層設計しないとデバッグ作業がし辛く、第三者が見たときに分かり難い記述になってしまいます。そのため、FPGAを設計するときは、階層設計することを心掛けることが重要です。

モジュール設計

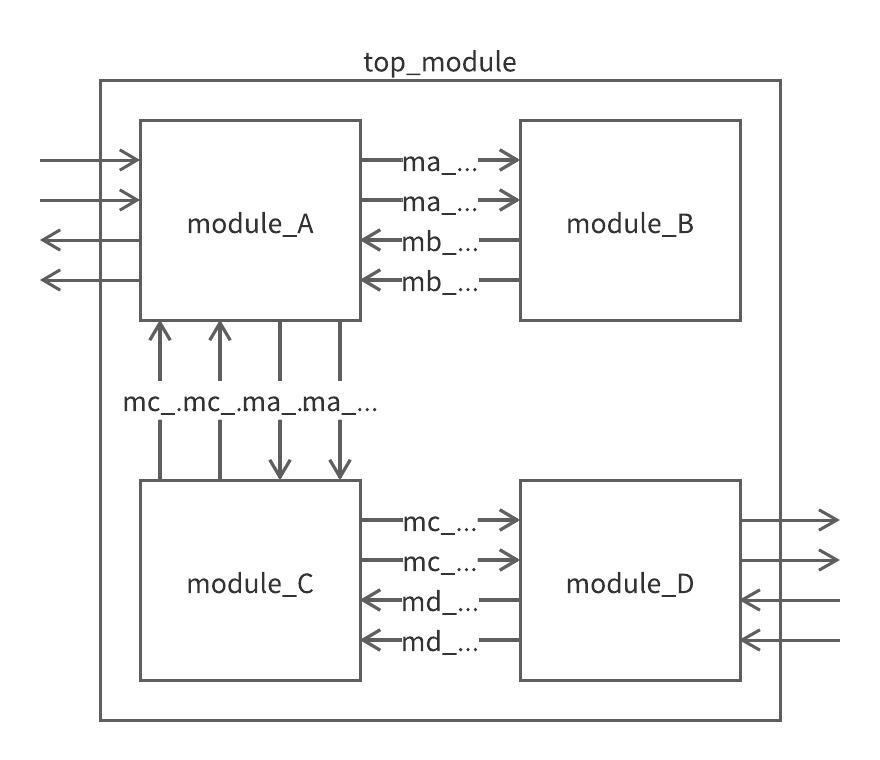

図3にモジュール設計したトップモジュールのブロック図を図示しています。モジュール設計の注意点を以下に列挙します。

- モジュール化は、基本的には仕様設計の段階で行います。仕様設計の段階でトップモジュールのブロック図を作成し、各モジュール間の結線情報を決定します。

- セレクタ回路や演算回路などのコンポーネントを複数個使用する場合、同じ機能を持つコンポーネントの記述はモジュール化します。デバッグでミスに気付いた場合、1個のモジュールを変更するだけで修正対応が可能です。

- 図3のように、出力先が明確になるようにワイヤ名を命名します。例えば、モジュールAから出力されているワイヤ名は、先頭が”ma”になっています。これは、デバッグのときに信号の出力先を確認する際に大変役に立ちます。