FPGA講座-7 D型フリップフロップ

フリップフロップとは

同期回路で重要な回路にフリップフロップがあります。フリップフロップとは、1ビットのデータを記憶できる回路です。フリップフロップには色々な種類が存在しますが、その中で最もよく使用されるD型フリップフロップについて説明します。

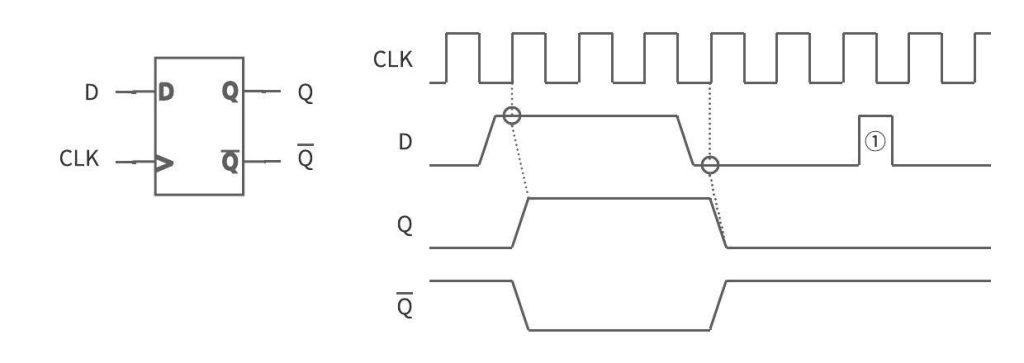

D型フリップフロップには、図1のようにクロック入力であるCLK端子、データ入力であるD端子、データ出力であるQ端子、その反転出力であるQバー端子があります。D型フリップフロップの特徴として、クロックの立ち上がりエッジで入力DのデータをラッチしてQに出力します。そのため、D入力が変化しても、次のクロックの立ち上がりまで出力Qは変化しません。図1の①のように、クロックの立ち上がりエッジに無関係なデータの変化に出力Qは影響しません。

D型フリップフロップの動作原理

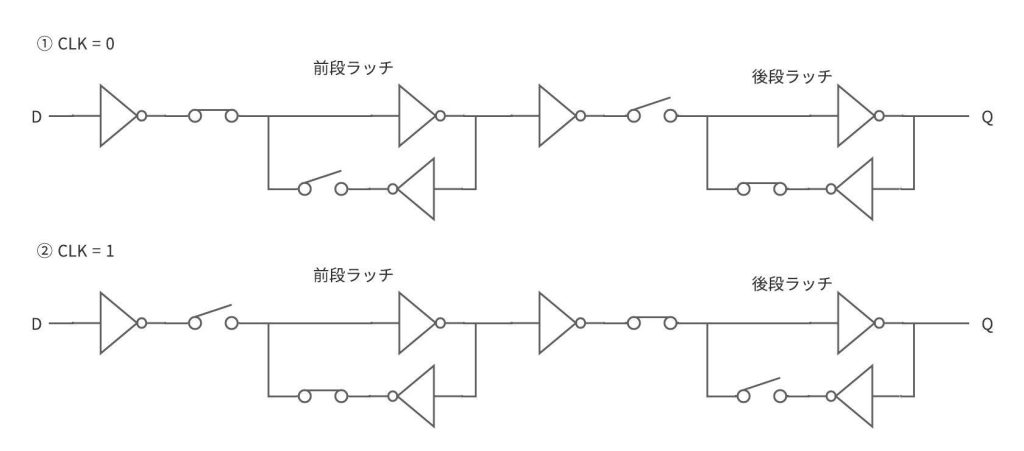

フリップフロップは、図2に図示したインバータループで構成された、2個のラッチ回路で構成されています。クロックが”0”のときは、後段ラッチ回路で前に取り込んだデータを保持します。そのため、入力Dの値が変化しても、出力Qは変化しません。クロックが”1”のときは、前段ラッチ回路で取り込んだ入力Dのデータを後段ラッチ回路へ伝搬しています。FPGA講座⑥ メタステーブルとチャタリング で説明したメタステーブルは、このインバータループでデータが一周していない状態のときに、このスイッチをオフしたときに発生します。

例えば、クロックが”0”のときに、入力Dから”1”が入力されていた場合、この前段ラッチ回路のインバータループの出力は”1”になっています。その時点でクロックが”1”になれば、インバータループは”1”のデータを回すことができ、出力Qに”1”を出力することができます。ところが、入力Dが”0”から”1”に変化した途端にクロックが”1”に変化した場合、インバータループには前の値である”0”が残っています。しかし、入力Dからは”1”が入力されているため、この箇所でデータ”0”と”1”が衝突してしまいます。そのため、中間電位となってしまい、メタステーブルが発生してしまいます。これがセットアップ時間が必要な理由であり、セットアップ時間とはインバータループを一周回る時間になります。

また、クロックが”1”になる前に、つまりはこのスイッチがオンになる前にデータが切り替わると、次のサイクルで取り込まれるデータを速く取り込んでしまったり、インバータループで発振したりする懸念があるため、ホールド時間の制約があります。

【参考文献】(※1)FPGAの原理と構成 8ページ オーム社(2016年)