FPGA講座-8 module文とポート宣言

Verilog HDLのプログラム構造

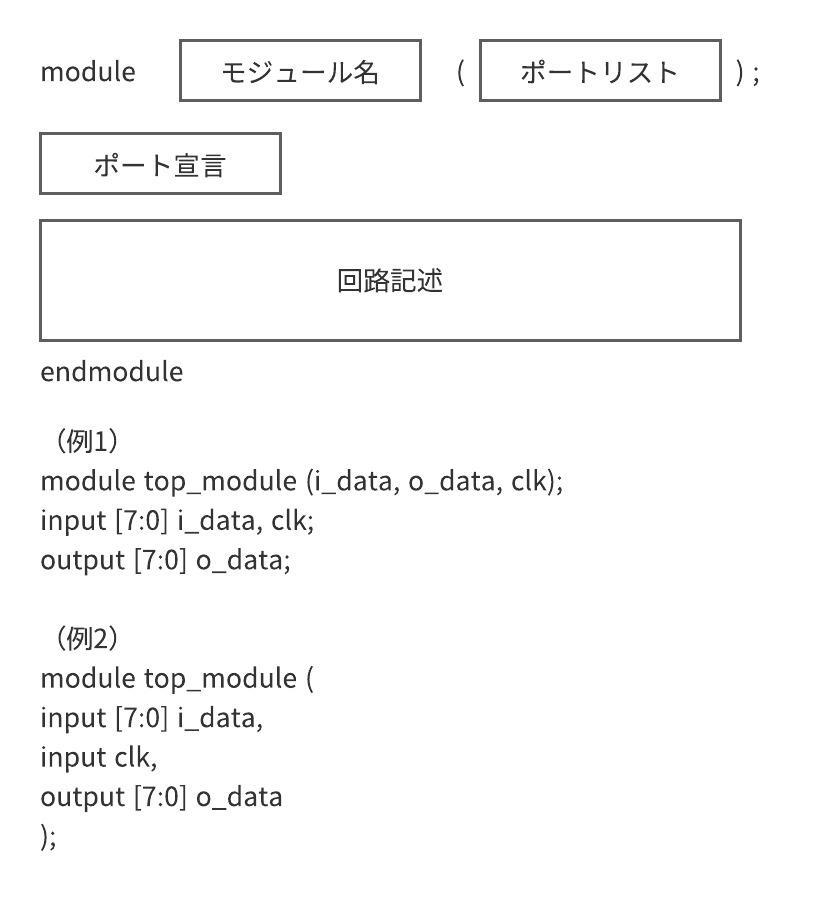

ハードウェア言語であるVerolog HDLは、FPGA講座-5 階層設計とモジュール設計 で説明した通り、プログラムをモジュール単位で記述します。このモジュールを定義する場合、図1のようなmodule文を使用します。

module文は、最初から順番にモジュール名、ポートリスト、ポート宣言と回路記述を記入します。そして、module文の最後には”endmodule”で終了するというルールがあります。

モジュール名は、例1、例2に示したmodule文では”top_module”になります。このモジュール名は、アルファベット、アンダーバー、数字で記述します。ただし、”module”、”endmodule”、”input”、”output”などの予約語は、モジュール名として使用できません。また、モジュール名の最後を数字で終わることはできません。

ポートリストは、このモジュールへ入力、またはモジュールから出力される信号名を記入します。例1のmodule文では”i_data”、”o_data”、”clk”が信号名になります。また、この信号名はカッコ( )の中に記述し、セミコロン ;で終了します。

ポート宣言は、ポートリストに記述した信号線の属性やデータ幅を指定します。属性には、input(入力)、output(出力)の他にinout(入出力)で設定します。ただし、inoutはトップモジュールでのみ使用できます(内部モジュールでは使用不可)。例1のmodule文では、”i_data”と”clk”は入力、”o_data”は出力になり、”i_data”と”o_data”は8ビットの信号線になります。また、例2のmodule文のように、ポートリストの中でポート宣言を一緒に記述することが可能です。

wire文とreg文

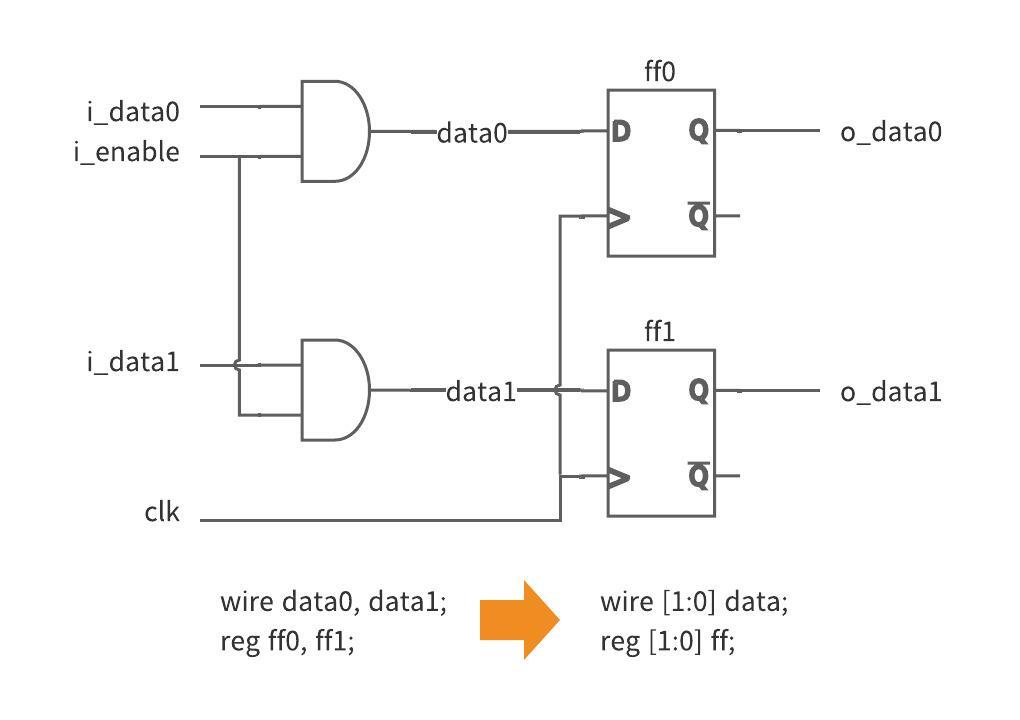

図1の回路記述で使用する、wire文とreg文について説明します。wire文は、モジュール間や回路の信号名を定義するときに使用します。図2において、AND回路とフリップフロップff0、ff1間に配線されている信号を”data0″、”data1″という信号名にする場合は、

wire data0, data1;

と記述します。”data0″と”data1″をまとめて記述する場合は、wire [1:0] data; と記述します。

reg文は、レジスタ名を定義するときに使用します。言い換えれば、図1のフリップフロップff0、ff1を定義するときです。この場合、

reg ff0, ff1;

と記述します。”ff0″と”ff1″をまとめて記述する場合は、reg [1:0] ff; と記述します。

図2のAND回路とフリップフロップff0、ff1を結線するときは、assign文を使用します。このassign文は、FPGA講座-9 assign文と条件式 で説明します。